Based on the system, a new type of configuration program is developed by using Verilog language. The output channels for clock are 14 and each channel for clock can also be configured for synchronizing, delay adjusting or calibrating. The system can provide the clock of low jitter which frequency is as high as 3.2 GHz. In this article, a programmable clock system of signal generation and distribution is designed for high‐speed acquisition system. The clock signal with low jitter is helpful to improve the signal‐to‐noise ratio (SNR) of sampled data and obtain high‐precision result.

The clock signal is the heartbeat of modern electronic system, and demands of increasing high‐quality signal has been raised, with the development of science and technology in the field of electronic information.

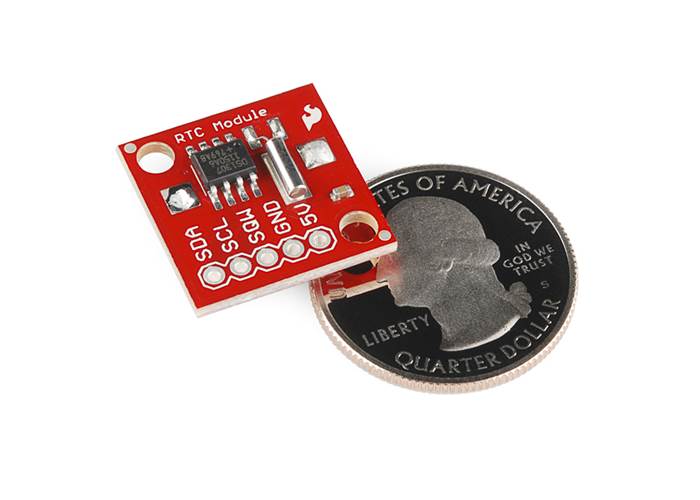

#Dclock real time clock series

Furthermore, we show that the upper bound of clock synchronization precision derived from our model holds for a series of experiments featuring native and virtualized setups. The results of our experiments illustrate that a type-1 hypervisor like ACRN implementing the dependent clock paradigm yields native clock synchronization precision. We present our implementation of a dependent clock for ACRN that can be synchronized to a grandmaster clock. Finally, we apply our insights to model the IEEE 802.1AS clock synchronization protocol and derive an upper bound on the clock synchronization precision of IEEE 802.1AS in a virtualized distributed real-time system. We discuss and model how virtualization, particularly resource consolidation versus resource partitioning, degrades clock synchronization precision. We use this formalization to propose a virtual clock condition that enables us to test the suitability of a virtual clock for the design of virtualized time-triggered real-time systems focusing on clock synchronization. We present a formalization of the notion of time in virtualized distributed real-time systems. A global time base results from clock synchronization with an upper bound on the clock synchronization precision. A prerequisite of time-triggered virtualization for hard real-time systems is providing access to a global time base to VMs and the hypervisor. A time-triggered hypervisor that activates virtual CPUs according to a global schedule can provide the means to allow for a resource-efficient implementation of the time-triggered paradigm in virtualized distributed real-time systems. Time-triggered communication and computation can act as an enabler of safe hard real-time systems.

Thus, VRI and PDP1, together with dClock itself, comprise a second feedback loop in the Drosophila clock that gives rhythmic expression of dClock, and probably of other genes, to generate accurate circadian rhythms.Virtualization of distributed real-time systems enables the consolidation of mixed-criticality functions on a shared hardware platform, easing system integration. Rhythmic vri transcription is required for molecular rhythms, and here we show that the clock stops in a Pdp1 null mutant, identifying Pdp1 as an essential clock gene. Repression of dClock by VRI is separated from activation by PDP1 since VRI levels peak 3-6 hours before PDP1. We show here that VRI and PDP1 proteins feed back and directly regulate dClock expression. vrille (vri) and Par Domain Protein 1 ( Pdp1) encode related transcription factors whose expression is directly activated by dCLOCK/CYCLE.

dClock is also rhythmically transcribed, but its regulators are unknown. In one loop, dCLOCK/CYCLE activates period expression, and PERIOD protein then inhibits dCLOCK/CYCLE activity. The Drosophila circadian clock consists of two interlocked transcriptional feedback loops.

0 kommentar(er)

0 kommentar(er)